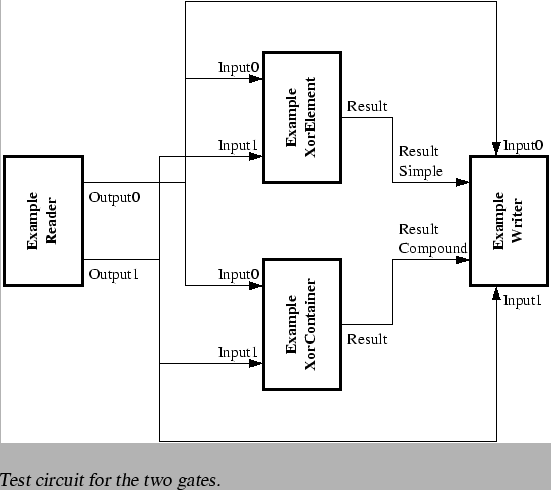

Two different ways to model an exclusive-or gate have been written. One using a simple ProcessElement, and the other by building up an xor from five component `and', `or' and `not' gates. These are called ExampleXorElement and ExampleXorContainer respectively. Note that the second compound-type gate would probably be a rather unwieldy and inefficient way to model the `xor' gate, but it is done this way to illustrate the construction of a ProcessContainer. It does however make apparent the fact that both classes have the same interface, both at the programming level and at the simulation level - ie they appear to have the same inputs and outputs and exhibit the same behaviour.

In order to test these two gates, we need to provide test-vectors, which

is done by reading a file through a ProcessReader called ExampleReader.

The results are output via a ProcessWriter called ExampleWriter. The

whole simulation is controlled by the steering class called ExampleMain.

Thus an example of user derived versions of all the main modeling

classes is given, plus the usage of BoolPorts to connect them is shown.

The simple test `circuit' is shown in figure 5.1. The

connections and input and output names are given for each of the ports.

The ExampleWriter receives both the inputs and the two gates' outputs

in order to write out a truth table for both.