# DPS to FEX Mappings: Interactions with LAr

Murrough Landon 31 October 2013

- Mappings

- •HEC (EMEC fwd) options

- •Optical plant (patch panels)??

- Link speed decision timetable?

- •Remapping in FPGAs: resource/latency?

## Basic Mapping Assumptions

- Two cases: EM layer to eFEX and the rest

- Two possible links speeds: 6.4 Gb/s or O(10) Gb/s

- •Baseline 6.4 Gb/s scheme (128 bits per BC)

- •EM supercells to eFEX: two towers per link 0.2\*0.1 in eta\*phi

- •20 supercells per fibre with roughly 10 bits/supercell

- •BCMUX scheme required to cope with this (not universally favoured!)

- •EM tower sums to jFEX, hadronic towers to both FEXes

- •Eight towers per fibre 0.4\*0.2 in eta\*phi

- Higher speed ambition (either 9.6 or 11.2 Gb/s?)

- •192 (or 224) bits/BC at 9.6 (or 11.2) Gb/s

- •EM supercells: same 0.2\*0.1 geometry, no need for BCMUX

- Though 20 supercells in 192 bits is a squeeze

- •EM jFEX and hadronic towers: 16 towers/fibre (0.8\*0.2?)

- •Fewer fibres even when increasing jFEX environment to 1.7\*1.7

#### Interactions with LAr

- Basic mapping layout agreed (FEX fibre geometry)

- •EM barrel/endcap crack handling seems OK in DPS

- To be confirmed after feedback from Fibernet?

- ·NB extra connector & pigtails on all AMCs just to cope with overlap region

- Ongoing discussion about EMEC forward and HEC

- Fanout for eFEX & jFEX requires inefficient use of HEC DPS

- ·Or else plenty of passive optical splitting

- Two proposals

- Merge HEC and EMEC-forward DPS (four partly under used modules)

- Merge EMEC-forward with EMEC-standard (making fully used modules),

double up separate HEC DPS (four very lightly used modules)

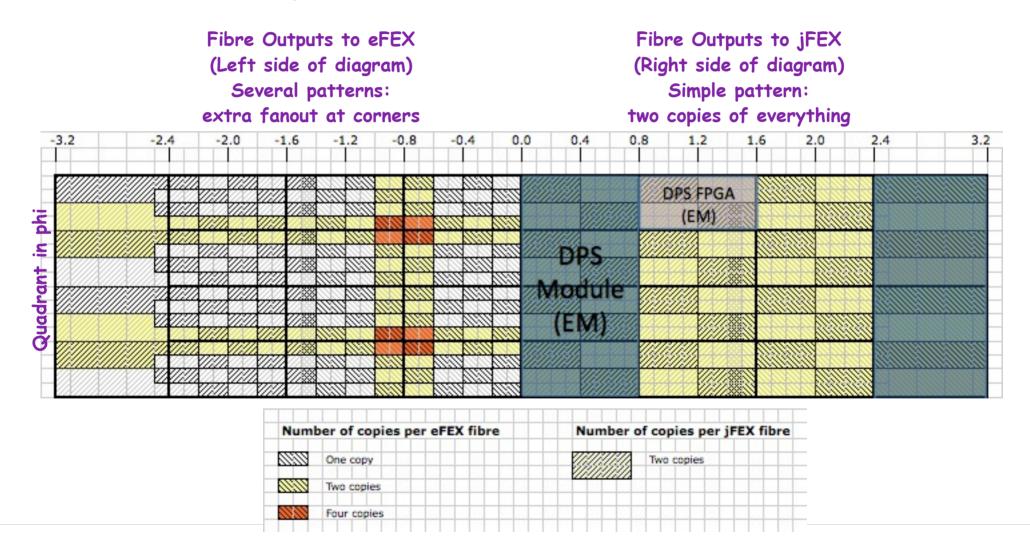

# DPS Fibre Outputs EM (1)

- Diagrams from set of spreadsheets...

- ·Shown for one quadrant

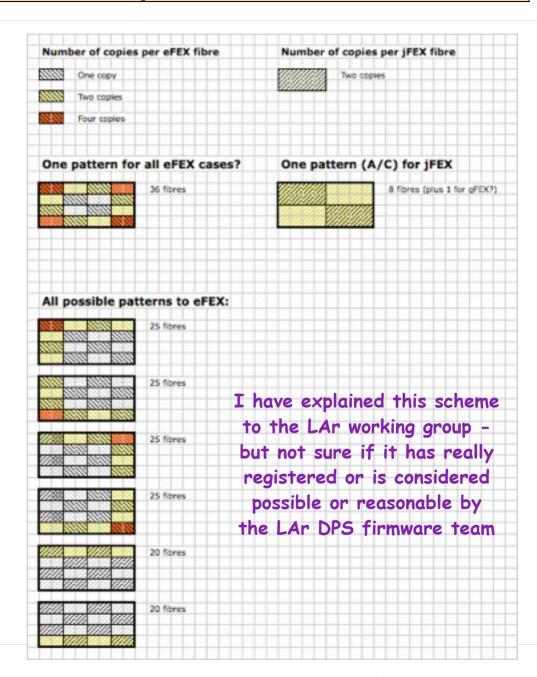

# DPS Fibre Outputs EM (2)

- Aim for single firmware for central EM DPS

- •OR of the six different eFEX patterns

- Uses 36 outputs (no more than 25 needed for any single pattern)

- Switch off unused outputs to save power

- Also 8 outputs for jFEX

- Only 6 at 10 Gbit/s (each fibre covers twice the area but three copies for 1.7\*1.7 jets)

- •1 output for gFEX

- Total 45 (of 48 available)

## DPS-FEX Optical Plant

- Least understood part of the system?

- ·Will there be any unexpected constraints from it?

- Number of optical connections, impact on optical power?

- ·Helpful to have a strawman design for this soon

## Link Speed Decision?

- Many things depend on link speed choice

- Number of output fibres (more towers/fibre)

- Possible jFEX environment

- Detailed mappings

- •DPS output arrangement for all tower fibres

- •In particular choice of DPS HEC/FwdEMEC arrangement

- ·At higher speeds some arrangements can avoid any passive optical splitting

- Work on filters

- ·Wiener filter only appropriate if no BCMUX

- · How long do we need to carry both options forward?

#### Remapping in DPS AMC FPGA

- ·LAr TDR states "remapping in DPS is easy"

- •I hope this is really true

- Would be good to estimate the FPGA resource impact of remapping DPS AMC inputs to output patterns for FEXes

- Are different firmware variants required?

- ·Surely need several radically different remappings

- •EM barrel, EMEC standard, EMEC special + HEC, FCAL

- Do these need different DPS AMC firmware bit files?

- •If so, would LAr have a scheme to load the right one automatically?

- •Or can the remapping be configured (without latency impact!)

#### Summary

- ·Mapping discussions with LAr ongoing

- · Various ideas for handling HEC and forward EMEC

- ·Need to estimate impact of remapping on firmware resources

- Early decision on link speed desirable

- ·Otherwise we have to keep multiple options alive

- •We need a clearer picture of what the optical plant is going to look like...